# NEUVIEME COLLOQUE SUR LE TRAITEMENT DU SIGNAL ET SES APPLICATIONS

NICE du 16 au 20 MAI 1983

COEFFICIENT ACCURACY AND ERROR ACCUMULATION IN STORED PRODUCT DIGITAL FILTERS

Daniel DUBOIS\* and Willem STEENAART\*\*

- \* Department of Electrical Engineering, Royal Military College, Kingston, Canada

- \*\* Department of Electrical Engineering, University of Ottawa, Ottawa, Canada

#### **RESUME**

L'importance de la méthode de filtrage numérique à produits stockés est montrée comme un moyen d'obtenir une plus grande précision des coefficients de filtrage, parce-que les produits stockés sont précalculés avec grande précision.

Les seuls erreurs présentes sont celles des produits stockés et elles sont controllables par le choix de longeur de mot. En conséquence il n'y a pas une grande augmentation d'erreur avec celle de facteur de qualité du résonateur numérique. Ceci nous donne un avantage en faveur du filtrage à produits stockés, puisqu'il est moins sensible relativement à sa structure en comparaison avec les filtres utilisant des multiplicateurs.

#### SUMMARY

The importance of the Stored-Product Digital Filter technique is emphasized as a means to achieve high coefficient accuracy, as the stored products are computed initially with high precision. This leaves only the product roundoff errors which can be controlled by the choice of the product wordlength. As a consequence the stored-product realization of digital filter resonators shows little increase in error with an increasing Q of the pole-pair. This indicates the stored-product filters to be less sensitive to structure than filters with multipliers.

Support from the Natural Sciences and Engineering Research Council under Grant A8572 and Strategic Grant G0665 is gratefully acknowledged.

### INTRODUCTION

The stored-product digital filter (SPDF) architecture, as formulated in [1] and [2] is a technique for achieving the highest possible processing speed [3], [4] along with reduced power consumption. The architecture makes use of Read Only Memory element (ROM) to store all possible products.

The purpose of this paper is to show that in addition to high speed, the SPDF also has the great advantage that no errors due to finite coefficient wordlength are introduced, as the products stored are based on near infinite wordlength coefficients. This has its consequences, as coefficient round-off does not take place, and the transmission function magnitude and the pole and zero locations are essentially unchanged from the given design values.

A similar, but not identical, effect occurs for the filters with distributed arithmetic [5], [6], where all binary sums of the coefficients are formed before the rounding of the sums; and subsequent additions create the overall sum of products.

For the SPDF the errors in the output are essentially resulting from finite signal and product wordlength and thus can be seen to contribute to the overall error accumulation in the regular manner. As the product wordlength can be increased, at little cost, further accuracy improvement can be obtained.

### COEFFICIENT WORDLENGTH IN BINARY MULTIPLICATION

In software as well as in hardware digital system implementation, the coefficient and signal values are both quantized by rounding or truncation. But there is an important difference in performing a multiplication with a digital multiplier or with the stored-product technique.

Daniel DUBOIS and Willem STEENAART

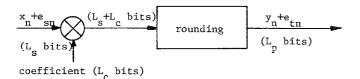

In a digital multiplier (fig. 1) the output signal is the truncated or rounded product of the input signal represented by L bits and of a coefficient represented by L bits. An important problem is to choose the coefficient

wordlength  $\mathbf{L}_{\mathbf{c}}$  as short as possible to minimize the hardware complexity and simultaneously as long as possible to minimize the perturbations introduced in the transfer function.

Fig. 1 - Multiplication operation by a digital multiplier

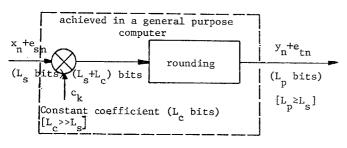

For stored-product multiplication the coefficient wordlength is very long compared to the signal and product wordlengths and this reduces the requirement for finding structures of minimal sensitivity to coefficient wordlength.

The procedure for multiplication in the SPDF is different, as at the design stage of the filter all possible products of the input signal of length  $\boldsymbol{L}_{\boldsymbol{S}}$ bits are calculated, corresponding to a coefficient of  $\rm L_C >> \rm L_S$  bits, rounded to  $\rm L_p$  bits and stored in the read-only memory (ROM) for that coefficient. The procedure used for the computation of these products is shown in fig. 2. As the computer accuracy allows  $L_c \gg L_s$ , the coefficient quantization effect is hereby reduced to an arbitrary low level.

Fig. 2 - Multiplication procedure used for programming the ROM element

Comparing the errors after the product rounding in each case gives some information on how the storedproduct technique helps in reducing the error. The total product error of the multiplier of fig. 1 is:

$$y_n + e_{tn} = (x_n + e_{sn})(c_k + e_{ck}) + e_{pn}$$

(1)

and

$$e_{tn} \approx e_{sn} c_k + e_{ck} x_n + e_{pn}$$

(2)

For the stored-product multiplication of fig. 2 the error becomes:

$$y_n + e_{tn}' = (x_n + e_{sn}) c_k + e_{pn}$$

(3)

and

$$e_{tn}^{\prime} \approx e_{sn} c_{k} + e_{pn} \tag{4}$$

In (1) - (4)  $e_{sn}$  is the signal roundoff error,  $e_{ck}$  the coefficient roundoff error and  $e_{pn}$  the product round-

Taking  $R_{em} = e_{tn} \cdot e_{t(n+m)}$  in both cases and evaluating the functions at m = 0 yields the total mean square error; for binary multiplication:  $R_{e}(0) = e_{ck}^{2} \frac{7}{x_{n}^{2}} + c_{k}^{2} \frac{e^{-2}}{s_{n}^{2}} + e_{pn}^{2} \qquad (5)$

$$R_{e}(0) = e_{ck}^{2} \frac{x}{x_{n}^{2}} + c_{k}^{2} \frac{e_{r}^{2}}{e_{sn}^{2}} + e_{r}^{2}$$

(5)

and for stored-product multiplication

$$R_{e}'(0) = c_{k}^{2} \overline{e_{sn}^{2} + (e_{pn}')^{2}}$$

(6)

The usual assumption has been made regarding the independence of the round-off noise sources.

The effect of signal round-off can be considered independent of the coefficient and product round-off and is dealt with in the sense that it contributes a known noise power at a filter's output for a given signal input power. For the single multiplier the term can be removed, assuming the applied signal of length  $\boldsymbol{L}_{\boldsymbol{S}}$  is accurate. Then:

$$R_e(0) = e_{ck}^2 \frac{x^2}{x_n^2} + \frac{2}{e_{pn}}$$

(7)

and

$$R_{e}(0) = \overline{(e_{pn}^{\prime})^{2}}$$

(8)

Having neglected the second order error terms in (2) and (4), the round-off noise processes are additive. Although for a given coefficient  $c_k$  the  $c_k^2$  term is deterministic, consider a general ck with the a roundoff error  $e_{ck}$  that has a uniform probability density function. In that case, for the multiplication (7) the overall error becomes  $R_{e}(0) = e_{ck}^{2} \cdot \frac{2}{x_{n}} + \frac{2}{e_{pn}^{2}} = \frac{2}{e_{ck}^{2}}$ (9)

$$R_e(0) = e_{ck}^2 \cdot x_n^2 + e_{pn}^2 = e^2$$

(9)

For equal wordlength coefficient and product  $(L_p)$  and  $x_n^2 = 1$ , the overall error (9) becomes

$$\overline{e^2} = \frac{2^{-2L}p}{6}$$

(10)

This is twice the mean square error obtainable from (8):

$$\overline{\left(e^{\,\prime}\right)^{\,2}}\,=\,\frac{2^{-2L}p}{12} \tag{11}$$

Furthermore, an increase in  $\boldsymbol{L}_{p},$  for the stored-product case can be seen to yield a reduced overall product round-off error, as this is the only contributing term in (11). For the multiplier error (9), an increase in  $L_{\rm p}$  only reduces the second term in the error, which will then be controlled by the coefficient round-off

To conclude, by examination of (10) and (11) and for = 1, we expect a 3 dB difference between a product with  $L_c=L_p$  from the binary multiplier, and a product with  $L_c>>\hat{L}_p$ , a stored-product. At the same time, for the stored-product the error will decrease by 6 dB every time  $L_{\text{p}}$  is increased by one bit, as is clear from (11). The evaluation of the accumulated error for second order filter sections confirmed these figures for the single multiplier.

## OVERALL FILTER OUTPUT ERROR

The error  $\overline{\mathbb{E}^2}$  on the output signal of a filter is defined as:

$$\overline{E^2} = \frac{1}{N} \sum_{n=0}^{N} (y_{\infty}(n) - y(n))^2$$

(12)

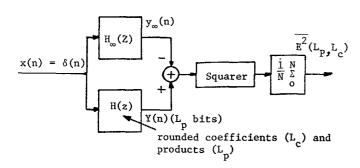

where y(n) respectively  $y_{\infty}(n)$ , is the rounded, respectively the ideal, output signal of a filter. J.B. Knowles and E.M. Olcayto [6] used a computational technique based on this definition for the evaluation of a coefficient quantization model. The system is represented in fig. 3; it has been applied to second order digital filter sections in the direct form.

Daniel DUBOIS and Willem STEENAART

Fig. 3 - Technique for measuring the error due to rounding

In fig. 3,  ${\rm H}_{\infty}(z)$  is the ideal transfer function of the filter.  ${\rm H}(z)$  has rounded coefficients of length  ${\rm L}_{\rm C}$  and the product is rounded to  ${\rm L}_{\rm p}$  bits. These wordlengths can be varied independently. For  ${\rm L}_{\rm C} \le {\rm L}_{\rm p}$  (H)z can be considered to be realized with binary multipliers and for  ${\rm L}_{\rm C} >> {\rm L}_{\rm p}$  with stored-product multipliers. The input signal  ${\rm x}_{\rm n} = \delta_{\rm n}$  is of variance one and contributes no error. All computations are performed in fixed point arithmetic and number quantization is by rounding.

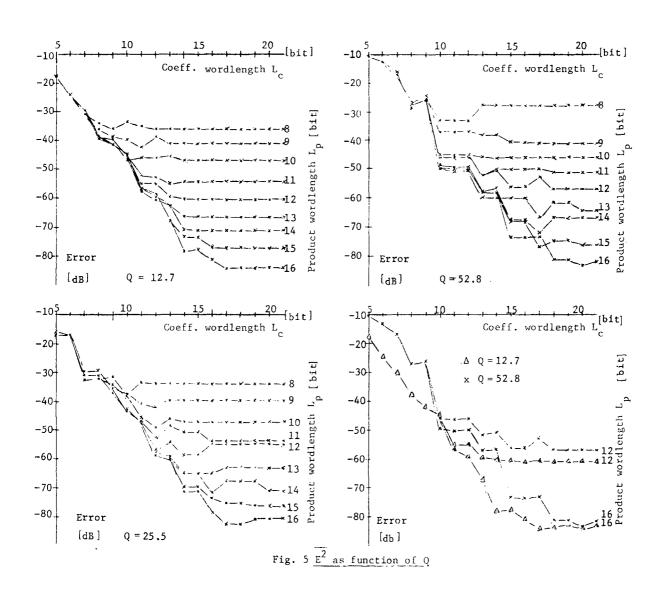

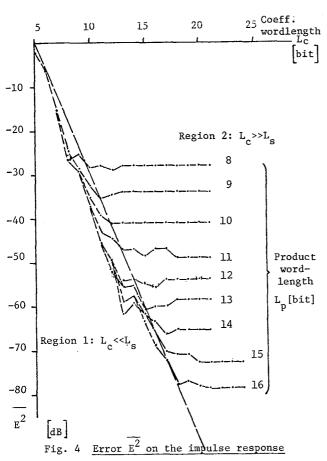

The resulting error  $\overline{L^2}$ , for several values of the wordlengths  $L_c$  and  $L_p$  is shown in fig. 4 for one second order filter section and in fig. 5 for three second order sections of different polepair quality factor (Q).  $\overline{E^2}$  is the result of an accumulation of errors in five products. In fig. 4 the two regions indicated separate the "binary multiplier filter" (region 1) from the "stored-product filter" (region 2). The points where  $L_c = L_p$  are  $\approx 3$  dB above the horizontal part of the curve for the same  $L_p$  value.

Increasing  $\mathbf{L}_{\mathbf{p}}$  gives an approximate 6 dB drop in accumulated error, as predicted for the single multiplier in the preceeding section.

For second order filter sections of different Q, as shown in figs. 5a-c the same pattern is maintained. In fig. 5d it is shown that the higher Q cases are more sensitive to wordlength for the multiplier realization than for the stored-product realization,as the horizontal parts of the curve are close in both cases ( $L_{\rm p}=12$  and  $L_{\rm p}=16$ ) considered. Although a complete analysis on the effects of stored-products addition still has to be made, it can be seen that the stored-product filter realization is very useful in the sense of minimizing overall error accumulation and of reducing the effect of sensitivity to coefficient wordlength.

#### CONCLUSION

The choice of the coefficient wordlength is one of the most important factors influencing the complexity and the accuracy in the hardware implementation of a digital filter using classical digital multipliers.

We have shown that this problem does not apply to SPDF's where the coefficient quantization effect is reduced to an arbitrary low value without any influence on the complexity of the filter.

This important property is of definite influence on the design of digital filters: As the coefficient quantization effect is eliminated the research for structures which minimize the sensitivity to wordlength of the coefficients is of lesser importance. The SPDF can be used in very simple structures, like the direct form, allowing for high speed applications [3].

In addition the application of memory elements is now attractive and will be even more attractive in the future, to replace digital multipliers.

#### BIBLIOGRAPHY

- [1] O. Monkewich and W. Steenaart, "Companding for digital filters", Proc. 1975 IEEE Int. Symp. on Circuits and Systems, ISCAS75, pp. 68-71.

- cuits and Systems, ISCAS75, pp. 68-71.

[2] O. Monkewich and W. Steenaart, "Stored-Product Digital Filtering with Nonlinear Quantization", Proc. 1976 IEEE Int. Symp. on Circuits and Systems, ISCAS76, pp. 157-160.

- [3] D. Dubois and W. Steenaart, "High Speed Stored-Product Digital Filters", IEEE Transactions on Circuits and Systems, vol. CAS-29, pp. 390-393, June 1982.

- [4] W. Steenaart, D. Dubois and O. Monkewich, "Stored-Product Digital Filtering", European Conference on Circuit Theory and Design, The Hague, August 25-28 1981. Conference Proceedings pp. 118-126.

- [5] A. Peled and B. Liu, "A New Hardware Realization of Digital Filters", IEEE Trans. Acoustics, Speech, Signal Process., Vol. ASSP-22, pp. 456-462, Dec. 1974.

- [6] K.D. Kammeyer, "Quantization Error Analysis of the Distributed Arithmetic", IEEE Trans. on Circuits and Systems, Vol. CAS 24, pp. 681-689, Dec. 1977.

- [7] J.B. Knowles and E.M. Olcayto, "Coefficient Accuracy and Digital Filter Response", IEEE Trans. on Circuit Theory, Vol. CT-15, pp. 31-41, March 1968.

# COEFFICIENT ACCURACY AND ERROR ACCUMULATION IN STORED PRODUCT DIGITAL FILTERS Daniel DUBOIS and Willenm STEENAART