## HUITIEME COLLOQUE SUR LE TRAITEMENT DU SIGNAL ET SES APPLICATIONS

NICE du 1er au 5 JUIN 1981

LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

C.MICHEL (1) J.LENFANT (2) F.BOERI (3) M.AUGUIN (3)

(1) SINTRA-ALCATEL 26 rue Malakoff 92600 ASNIERES (2) IRISA Campus de BEAULIEU RENNES

(3) LASSY-Université de NICE ERA835CNRS 41 bd Napoléon III 06041 NICE Cedex

#### RESUME

# <u>Résumé</u>: Avec l'intégration de plus en plus poussée des composants électroniques (1 million de composants sur une seule "puce" de silicium), l'intérêt des systèmes parallèles multifonctions ne fait que croître.

- Les processeurs spécialisés dans le traitement du signal (AMI, INTEL) ou encore les macro fonctions de base tel que papillon de FFT, filtres, permettent d'imaginer de nouvelles architectures de machines qui permettraient d'utiliser de façon efficace un grand nombre de ces composants qui participeraient tous au même traitement (Sonar, radar, ...).

- Un des problèmes technologiques les plus délicats à résoudre est celui du système d'interconnexion entre ces modules.

- En effet, la solution bus unique ne possède pas la bande passante nécessaire.

- Les autres systèmes de communications tels que la matrice "cross-bar" ou les systèmes multibus représentent un volume de matériel considérable par rapport aux processeurs qui y seraient abonnés (le coût croît comme le carré du nombre d'abonnés).

- Nous présentons dans cet article d'autres types de réseaux d'interconnexion ayant un coût beaucoup plus limité (réseau de Bènes, réseau Ω, réseau triangulaire de Brassard) qui sont réalisables à partir d'un circuit intégré spécifique original (logique multivaluée, et technologie subnanoseconde) conçu par SINTRA-ALCATEL et réalisé par les laboratoires de MARCOUSSIS et de contrôleurs répartis ultra rapides.

Les caractéristiques et performances de cette nouvelle fonction d'inter-communication (consommation, encombrement, débit d'échanges) sont précisées.

#### SUMMARY

As electronic components are getting more and more integrated (I million elements on a single silicium chip), interest in multifonctions parallel systems does not cease increasing.

Components dedicated to signal processing (AMI, Intel) or other basic macrofunctions such as FFT, butterfly, filters, allow to imagine new architectures for machines leading to the efficient use of a large number of these components which would perform the same processing (Sonar, Radar...)

On of the most délicate technological problem is to interconnect these modules. For a single bus system does not give sufficient throughput.

Other communication systems such as cross-bar matrix or multibus systems leads to a considerable amount of hardware, with référence to the number of subscribers (cost increases like the number of subscribers to the square).

In this paper, we describe other types of interconnections networks, having a lower cost (Bénes network,  $\Omega$  network, Brassard's triangular network...) wich can be implemented with a specific original integrated circuit (multivalued subnanosecond logic) designed by SINTRA-ALCATEL and manufactured by LABORATOIRES DE MARCOUSSIS, along with distributed high speed controlers.

Some features and performances of this new interconnecting function (power, volume of hardware, interchange flow  $\dots$ ) are given.

(\*) Cette étude est soutenue par la Direction à la Recherche et aux Etudes Techniques (DRET) Contrats (79/420, 79/422, 80/080, 81/200).

- LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

#### 1 - INTRODUCTION

$L^{\dagger}$ augmentation des performances en vitesse de traitement des systèmes numériques se heurte à une barrière infranchissable qui est la vitesse de propagation des porteurs dans les conducteurs.

Des technologies subnanoseconde (ECL 100K, arseniure de gallium, effet Josephson) pousseront de plus en plus loin ces limites.

Toutefois le faible rendement de ces technologies (quelques centaines de portes par circuit, avec une consommation et un prix élevé) devient vite une contrainte pour réaliser des systèmes à hautes performan-

De plus, les besoins actuels en matière de puissance de calcul pour le traitement du signal ne font que croître (autrement dit : pour un prix donné on arrive toujours à imaginer des algorithmes de plus en plus sophistiqués).

La caractéristique essentielle de ces traitements est qu'un parallélisme important peut être mis en oeuvre sans apport notable "d'overhead".

Ainsi il parait souhaitable d'utiliser des technologies très intégrées (HMOS) et de posseder des outils permettant de faire coopérer les différents modules (en général processeurs) sur le même algorithme.

Ces outils se situent à la fois au niveau des communications (chemins des données) et du contrôle (synchronisations, allocations de ressources, ordonnancement, ...).

Il est remarquable de noter que le traitement parallèle peut se faire en général en mode vectoriel (S.I.M.D.), ce qui est toujours plus efficace lorsque les traitements s'y prêtent (ex : filtrage, FFT, tri, travail sur matrices).

Toutefois, en bout de chaîne, les flots deviennent moins réguliers et la coopération ne devient efficace qu'en mode M.I.M.D  $^2$ , (Normalisation SONAR, reconnaissance des formes, intelligence artificielle).

Dans les deux modes de fonctionnement SIMD et MIMD, un problème crucial qui se pose est celui du support de communication entre les processeurs élémentaires. En effet les systèmes à bus unique deviennent vite limités en débit et sûreté de fonctionnement, alors que les systèmes de communication plus sophistiqués de type mémoires multiports (ou matrice "cross-bar") impose un coût (volume de matériel, prix, fiabilité, consommation...) beaucoup trop élevé lorsque le nombre de processeurs dépasse la dizaine.

Nous présentons ci-après, d'autres systèmes de communications qui rendent plus compétitives les architectures multiprocesseurs.

#### 2 - LES RESEAUX D'INTERCONNEXION

#### 2.1 - INTRODUCTION

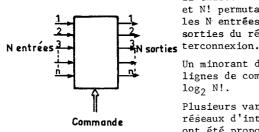

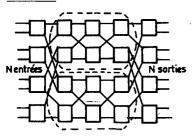

Il existe NN relations et N! permutations entre les N entrées et les N sorties du réseau d'in-

Un minorant du nombre de lignes de commande est  $log_2$  N!.

Plusieurs variantes de réseaux d'interconnexion ont été proposées en fonction des contraintes: de dimension, modularité,

débit, compléxité de gestion, survivabilité ...

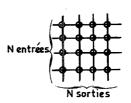

Le premier réseau d'interconnexion connu et conceptuellement le plus simle est la matrice de points de croisement. Ce réseau comporte  $\mathbb{N}^2$  commutateurs (ce qui devient prohibitif lorsque N dépasse 16 en général).

Cette matrice peut effectuer toutes les permutations de N entrées sur N sorties soit N! permutations (sa bande passante croit linéairement avec N-La Bande Passante et le mombre de connexions établies par unités de temps).

Toutefois pour un réseau construit à partir de commutateurs à deux états, le nombre nécessaire de commutateurs est minoré par log2 N! (fonction équivalente à N log2 N d'après la formule de STIRLING :

$$N! \simeq \left(\frac{N}{e}\right)^N \sqrt{2\pi N}$$

Ainsi la matrice de N<sup>2</sup> points de croisements est donc excessivement coûteuse ; par conséquent d'autres réseaux d'interconnexion ont été imaginés.

#### 2.2 - CLASSIFICATION DES RESEAUX D'INTERCONNEXION

Un grand nombre de réseaux d'interconnexion ont été proposés ces dernières années avec le souci constant de réduire ce nombre de commutateurs à 2 états. Ils peuvent se regrouper essentiellement en trois catégories :

#### 1 - Les réseaux sans blocages

Entre une entrée inactive et une sortie inactive, il existe toujours un chemin ne necessitant pas la modification des chemins déjà établis.

#### 2 - Les réseaux réarrangeables

reposent sur une affaiblissement de cette contrainte vers une entrée inactive et d'une sortie inactive, il est toujours possible de trouver un chemin mais l'établissement de celui-ci peut entrainer un reroutage des autres liaisons établies (les N! permutations sont donc toutes possibles).

#### 3 - Les réseaux avec blocage

des conflits non réductibles peuvent apparaître (les N! permutations ne sont pas toutes possibles). C'est le type de réseaux généralement utilisés en téléphonie, la probabilité d'un blocage y étant maintenue en dessous d'un certain seuil compte tenu du traffic prévu.

Chaque type de réseau peut être controlé suivant 2 modes:

- mode asynchrone (pour machines MIMD)

- mode synchrone (pour machines SIMD)

LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

#### 2.2.1 - Les réseaux sans blocages

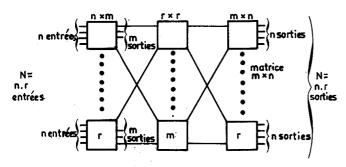

Dans cette catégorie nous trouvons les matrices à  $N^2$  points de croisement et le réseau de Clos (1953) :

Ce réseau est sans blocages si et seulement si m  $\geqslant$  2n-1. Son coût pour n  $\cong$ r est donc de l'ordre de N $^3/2$ . Cantor (1972) a exhibé un réseau sans blocage de complexité N (logN) $^2$  tandis que Bassalygo et Pinsker (1974) ont montré l'existence théorique de réseaux asymptotiquement minimaux c'est-à-dire en NlogN.

#### 2.2.2 - Les réseaux réarrangeables

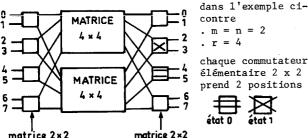

Si m > n le réseau de clos devient réarrangeable :

En continuant la construction itérative au niveau de chaque matrice de l'étage médian on obtient le <u>réseau</u> de Benès :

ce réseau possède (2 logN-1) étages de  $\frac{N}{2}$  commutateurs.  $\frac{N}{2}$  soit NlogN- $\frac{N}{2}$  commu-

tateurs. 2

son contrôle asynchrone est relativement complexe (i1

necessite O(NlogN)

pas de oalcul).

Réseau triangulaire de Brassard : (3)

il s'agit en fait de la moitié d'une matrice "cross-bar" le coût croit comme  $\frac{1}{2}$  (N^2-N)

#### 2.2.3 - Les réseaux avec blocage

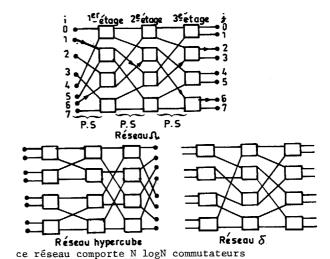

Plusieurs types de réseaux avec blocage ont été étudiés (réseau oméga, réseau delta, réseau hypercube, manipulateur de données, réseau ILLIAC, réseau ascenceur). Il s'agit au moins pour les trois premiers, de variantes du même réseau par rénumérotation des commutateurs :

La notion de "perfect shuffle (noté PS) (mélange parfait du bridgeur) que l'on retrouve d'ailleurs pour beaucoup d'algorithmes parallèles réalisés par procédés dichotomiques (FFT, tri, transpositions de matrice) permet d'imaginer que chaque sortie du réseau peut être connectée à chacune des entrées.

Le "perfect shuffle" (P.S) est une permutation définie comme suit :

$$i \xrightarrow{P.S} j$$

$i = numéro de l'abonné en entrée du P.S  $j = numéro de l'abonné en sortie du P.S$$

P.S (i) = 2i = j si

$$0 \le i \le \frac{N}{2} - 1$$

P.S (i) = 2i + 1 - N = j si

$$\frac{N}{2} \leq i \leq N - 1$$

Il est connu depuis longtemps que le "perfect shuffle" associé à une transposition constitue un système générateur d'un groupe symétrique d'ordre pair.

On vérifiera que si N = 8 et que si i est représenté par  $x_3$   $x_2$   $x_1$  en base 2 ;

exemple:

$$i = (6)_{10} = (110)_2$$

$x_3 = 1$

$x_2 = 1$

$x_1$ = 0 alors le passage à travers le "perfect shuffle",

réalise j = P.S (i) = P.S (

$$x_3 x_2 x_1$$

)=  $x_2 x_1 x_3$  = décalage circulaire de i

soit  $y_3$   $y_2$   $y_1$  la représentation binaire de la destination et soit  $x_3$   $x_2$   $x_1$  la représentation binaire de la course

Supposons qu'un réseau  $\Omega$  soit chargé d'établir cette connexion :

il suffit d'appliquer la commande  $x_3 \bigoplus y_3$  au commutateur rencontré au premier étage, les commandes  $x_2 \bigoplus y_2$  et  $x_1 \bigoplus y_1$  à ceux des étages suivants ; le routage est alors :

LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

Des conflits peuvent évidemment se produire.

On peut remarquer, par ailleurs, que le réseau de Benès n'est jamais qu'un assemblage d'un réseau oméga renversé et d'un réseau oméga direct !

#### 2.2.4 - Autres réseaux

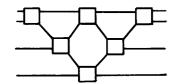

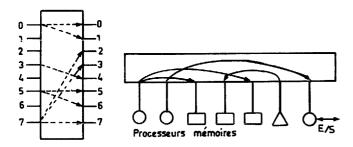

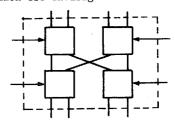

Citons rapidemment les réseaux multivoques qui permettent de connecter une entrée à un nombre quelconque de sorties ( $\mathbb{N}^{\mathbb{N}}$  relations), les réseaux à un seul côté qui permettent de connecter indifferemment les processeurs, les mémoires, les périphériques d'une manière entièrement banalisée.

réseau multivoque partionneur

réseau à un seul côté

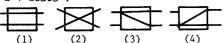

Si les réseaux à un seul côté sont généralement conçus à partir du commutateur à deux états précedemment défini, les réseaux multivoques necessitent un commutateur à 4 états :

## 3 - LES DIFFICULTES INTRODUITES PAR LES RESEAUX D'INTERCONNEXION

Les réseaux d'interconnexion n'ont suscité un vif intérêt que depuis peu, car de nombreuses difficultés ont dû être résolues.

#### 3.1 - VOLUME IMPORTANT DU MATERIEL

Le volume du matériel pour une matrice de points de croisement est démesuré par rapport aux abonnés.

A titre d'exemple une matrice "cross-bar" de 16 abonnés de 40 bits necessite 64 grandes cartes (format "europe" double) soit près de 1000 circuits intégrés.... Une telle approche n'est viable que si elle allie des structures combinatoires de complexité moindre à divers raffinements technologiques.

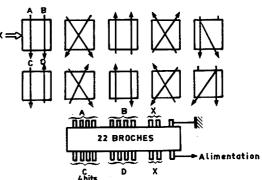

#### 3.2 - CONNECTIQUE

C'est le problème fondamental qui est en fait une butée. En effet, même si le nombre de circuits intégrés peut être réduit par une intégration de plus en plus poussée, le nombre de points de connecteur reste immuable et à la limite une carte à circuits imprimés ne comporte plus qu'un circuit intégré de 96 broches !....

#### 3.3 - LE RETARD

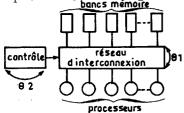

Le réseau d'interconnexion va souvent se retrouver entre mémoires et processeurs si bien que le retard  $\theta_1$  apporté par les rangées successives de commutateurs bancs mémoire intervient directement

intervient directement dans le temps d'accès à la mémoire.

L'intérêt du réseau d'interconnexion peut alors être largement compromis si ce retard est incompatible avec les temps de cycle des processeurs et des mémoires qui lui sont abonnés.

#### 3.4 - LA COMMANDE

La commande d'une matrice de points de croisements est relativement simple à réaliser. Celle des autres types de réseaux peut être très complexe aussi bien en mode synchrone qu'en mode asynchrone.

A titre d'exemple, le contrôle d'un réseau de Benès peut necessiter un véritable processeur (minicalculateur, microprocesseurs).

Si les temps d'établissement des chemins  $(\Theta_2)$  deviennent trop importants vis-à-vis du cycle des abonnés ; alors l'intérêt du réseau d'interconnexion reste limité (les applications en téléphonie notamment ne sont pas très contraignantes à cet égard, par contre pour une machine MIMD le calcul des chemins doit se faire en quelques dizaines ou quelques centaines de nanosecondes.

#### 3.5 - LA SURETE DE FONCTIONNEMENT

Le nombre important de composants et de liaisons va impliquer une fiabilité plus mauvaise que celle d'un simple bus. La possibilité de reconfiguration des réseaux d'interconnexion a sucité peu d'études jusqu'à présent. Notons que certains réseaux (comme le réseau  $\Omega$ ) ne possèdent qu'un seul chemin d'une entrée vers une sortie si bien que les méthodes de reroutage deviennent problématiques.

#### 4 - LES ETUDES A LA SINTRA-ALCATEL

Depuis plus de 3 ans des études et des réalisations ont entreprises à la SINTRA (en collaboration avec l'IRISA, le LASSY et l'université PARIS VI) pour mettre en oeuvre les réseaux d'interconnexion dans les systèmes informatiques à hautes performances.

Toutes les difficultés citées précédemment ont pu être en grande partie surmontées.

#### 4.1 - REDUCTION DU VOLUME DE MATERIEL

Réalisation d'un circuit MSI spécifique, assurant 10 fonctions de permutations, et pouvant fonctionner en mode bidirectionnel. Ce circuit commutateur élémentaire peut être utilisé dans tous les types de réseaux passés

Il est capable de remplacer 5 circuits intégrés.

L'intégration hybride de 4 puces commutateurs connectés en papillon est envisagée.

LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

#### 4.2 - DIMINUTION DE LA CONNECTIQUE

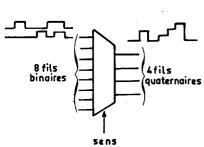

Le circuit décrit précédemment fonctionne en logique binaire; un deuxième circuit intégré MSI réalise les fonctions de transcodage entre logique binaire et logique MULTIVALUEE (4). Ce circuit n'est utilisé que pour diminuer le nombre de fils de liaison entre cartes; il transforme 8 fils binaires en 4 fils quaternaires. Le volume du matériel est ainsi potentiellement divisé par deux.

Les difficultés essentielles (qui ont été surmontées en développant une nouvelle technologie bipolaire) étaient : la conservation des marges de bruits des technologies classiques ECL; et la diminution de la consommation (qui devient très importante lorsque le courant augmente)

#### 4.3 - RETARD TRES FAIBLE

Les deux circuits décrits précédement sont réalisés dans une technologie ECL subnanoseconde. Un procédé spécial de fabrication permet d'obtenir pour chaque circuit un excellent "facteur de mérite" environ 10 pJoule contre 40 pJ pour l'ECL10K.

(soit 2m par Porte pour lns de temps de traversée).

#### Performances obtenues :

circuit : codeur/décodeur : 2ns de temps de traversée

0,5w de dissipation

circuit commutateur : 2,5ns et 0,35w

#### 4.4 - LA LOGIQUE DE COMMANDE

Plusieurs dispositifs de commande ont été étudiés et sont aujourd'hui en cours de réalisation.

## 4.4.1 - Commande rapide par réseau de Benès en mode asynchrone MIMD

Un algorithme original pour contrôler rapidemment le réseau de Benès, sans utiliser les reroutages, a été développé (5).

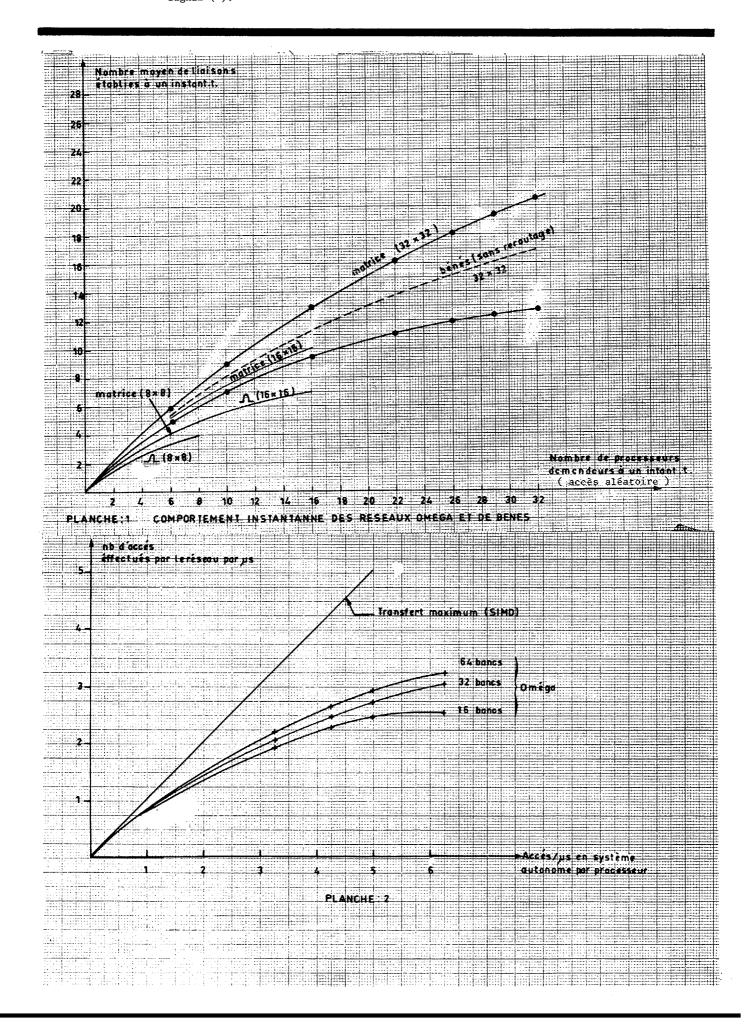

Des résultats de simulation ont montré que le débit d'un tel réseau de Benès est meilleur que celui d'un réseau  $\Omega(Planche~1)$ .

## 4.4.2 - Commande rapide pour réseau $\Omega$ en mode asynchrone MIMD

Une unité de commande câblée pour réseau  $\Omega$  a été réalisée (5). Sa structure très simple utilise des méthodes asynchrones (sans horloges). Le contrôleur est distribué au niveau de chaque commutateur élémentaire.

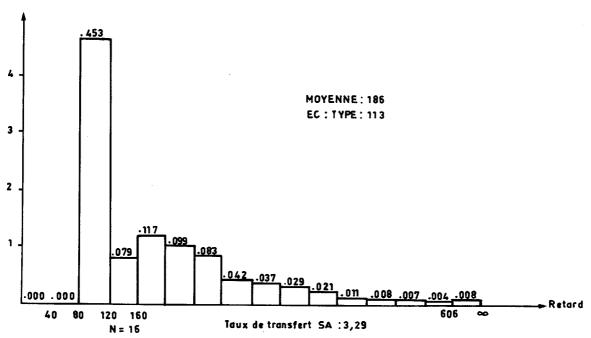

Les performances obtenues sont données sur les planches 2 et 3.

Notons qu'un simulateur logiciel de réseau  $\Omega$  a été conçu pour évaluer plusieurs politiques de commande.

## 4.4.3 - Commande rapide pour réseaux $\Omega$ et Benès en mode Synchrone MSIMD

La commande synchrone d'un réseau d'interconnexion pose des problèmes différents et en général plus complexes que les contrôleurs asynchrones. Un tel réseau se comporte comme un permutateur de données.

A chaque instruction élémentaire d'une machine SIMD, une permutation du réseau peut être demandée pour réaranger les données issues de la mémoire (ou encore pour échanger les informations entre processeurs élémentaires).

Une machine SIMD devient interessante lorsqu'elle comporte un grand nombre de processeurs élémentaires (P.E); ainsi pour 256 abonnés, la commande d'un réseau de Bènes nécessite l'élaboration de 1920 bits pour les 15 étages de 128 commutateurs élémentaires!.

Il n'est pas envisageable d'indiquer explicitement à chaque instruction, ilétat de chaque commutateur ...

Fort heureusement le nombre de permutations effectivement utiles, quoique considérable, est très petit vis-à-vis de N!.

Ces permutations ont été classées en familles et un algorithme recursif calqué sur la structure itérative du réseau de Bènes a été imaginé (7).

Une unité de commande de réseau Bènes (et $\Omega$ ) pouvant fonctionner en mode partitionné (c'est-à-dire : l seule machine SIMD à 256 P.E ou 2 machines SIMD asynchrones ayant chacune 128P.E ou 4 machines SIMD de 64 PE ...) est aujourd hui en cours de réalisation (8).

#### 4.5 - FIABILITE - SURETE DE FONCTIONNEMENT

Chaque commutateur élémentaire est réalisé avec des procédés de fabrication qui permettent d'obtenir une fiabilité environ 10 fois supérieure à celles des procédés classiques. L'intégration hybride des "puces" élémentaires ne fait qu'améliorer cette fiabilité.

Le MTBF prévu est de 10<sup>7</sup> heures par commutateur élémentaire (pour 4 bits).

Les aspects détection de panne et reconfiguration ont été considérés (9).

En environnement asynchrone le réseau  $\Omega$  pourra détecter en ligne ses propres pannes (au niveau du contrôle).

Une procédure hors ligne de localisation du commutateur défaillant est prévue, de plus une réconfiguration du système est possible en rebouclant les Sorties du réseau  $\Omega$  sur les entrées ou par insertion de commutateurs de secours.

En environnement synchrone l'autotest du contrôleur est prévu ; l'insertion de commutateurs de secours est alors la seule alternative.

#### 4.6 - RESULTATS DES MESURES ET PERFORMANCES OBTENUES

Un réseau  $\Omega$  de 16 abonnés est réalisé à partir de cartes au format 160x235 (europe). Il occupe 1 carte pour 4 bits de large ; 2 cartes pour 8 bits etc... La logique de commande est implantée sur 2 cartes.

Consommation par carte : 20w. Le temps de création d'un chemin est de 100ns lorsqu'il n'y a pas de blocages.

#### Performances en débit :

- Planche 1 - Comportement instantané des réseaux  $\Omega$ , Benès (sans reroutage) et Matrice de points de croisement lorsque les accès sont purement aléatoires.

- LES RESEAUX D'INTERCONNEXION - un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

- Planche 2 Influence du nombre de bancs réseau  $\Omega$  comportant 16 processeurs avec : 16 bancs, 32 bancs, 64 bancs mémoire.

- Planche 3 Distribution statistique des attentes d'accès aux bancs.

#### 5 - APPLICATIONS POSSIBLES DU TRAITEMENT DU SIGNAL

Plusieurs gammes d'applications sont aujourd'hui évaluées :

- couplage de plusieurs microprocesseurs monolithiques (HMOS) spécialisés en traitement du signal, réalisation d'une machine SIMD de forte puissance, mémoire parallèle multidimensions, opérateurs spécialisés ...

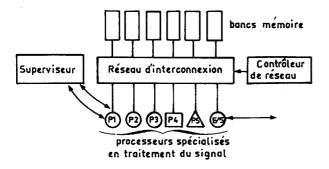

## 5.1 - COOPERATION DE PLUSIEURS MICROPROCESSEURS SUR LE MEME TRAITEMENT

La liaison étroite de plusieurs microprocesseurs monolithiques spécialisés en traitement du signal (INTEL, AMI ...) est dorénavant rentable dans la mesure ou l'on sera capable de réaliser un système de gestion des tâches concurrentes suffisemment performant.

Un tel superviseur réalisant les fonctions de synchronisation des tâches et d'allocation des ressources est en cours de conception.

Il repose essentiellement sur l'implantation d'un réseau de Pétri (10) dans un processeur spécialisé.

Le réseau d'interconnexion peut être utilisé en mode MIMD ou SIMD.

Le fonctionnement SIMD impose toutefois quelques contraintes pour les microprocesseurs monolithiques et une réalisation en microprocesseurs "par tranches" semble beaucoup mieux adaptée

## 5.2 - MACHINE SIMD DE FORTE PUISSANCE SPECIALISEE EN TRAITEMENT DU SIGNAL

Les limites (Souplesse, puissance, facilité de programmation...) des processeurs SIMD provenaient essentiellement de la puissance du réseau d'interconnexion ainsi par exemple le réseau des machines comme ILLIAC IV, DAP ou MPP ne permet de faire communiquer que des processeurs voisins (Nord, Est, Ouest, Sud) l'ascenseur du PROPAL réalise des décalages et permet des échanges très limités entre les P.E (d'ou une spécialisation poussée pour le traitement d'images).

Le réseau le plus puissant jamais réalisé (celui du STARAN) ne réalise que des permutations simples. Le réseau MSIMD en cours de réalisation permettra d'implémenter les algorithmes fréquement utilisés en traitement du signal avec un maximum d'efficacité:

- accès parallèle aux éléments d'une matrice par ligne, par colonne, par diagonale, par bloc carré, ...

- 2) permutations permettant de mettre en oeuvre des méthodes dichotomiques pour la création d'algorithmes (diviser un problème de taille N en deux problèmes de taille  $\frac{N}{2}$ ).

- 3) permutations de type "mélange parfait" qui permet de réaliser les algorithmes de type : FFT, tri, calcul d'un polynôme, transposition de matrice... en un minimum de passage à travers le réseau.

- 4) permutation réalisant des opérateurs de type APL sur des vecteurs de tailles quelconques en un nombre minimal de passage à travers le réseau : SELECTION

EXPANSION

INSERTION

EXCLUSION

SEPARATION

MASK

DIFFUSION...

Notons que ces primitives qui permettent notamment de gérer les grandes matrices creuses, incluent les fonctions de manipulation de données du CYBER 205.

L'utilisation d'un tel réseau comme opérateur d'accès d'une mémoire parallèle associé à des microprocesseurs bipolaires et des composants spécialisés comme ceux réalisés par TRW permettra d'atteindre des puissances de calcul jamais atteintes (plusieurs centaines de millions d'opérations par secondes).

#### 5.3 - STRUCTURES D'ACCUEIL POUR OPERATEURS SPECIALISES

Le Pré-Processeur de Signal (P.P.S)(11) réalisé à la SINTRA est un processeur microprogrammé qui peut recevoir sur ses 2 bus internes des opérateurs spécialisés (filtre, papillon FFT, Normalisation SONAR,...). Le réseau d'interconnexion peut réaliser une structure d'accueil plus performante qui autorisera le fonctionnement simultané de ces opérateurs. De plus le chaînagemenco "pipe-line") entre ces opérateurs peut être réalisé dynamiquement.

Le réseau d'interconnexion pourra être, bien entendu, utilisé pour coupler plusieurs PPS dans des architectures MIMD. Le partage d'une mémoire commune peut s'avérer indispensable dans certaines phases du traitement

#### 5.4 - MEMOIRES MULTIDIMENSIONS

Il s'agit d'une mémoire à débit relativement élevée et de forte capacité à laquelle on peut accéder par ligne, colonnes, diagonales, plans dans les 3 axes, cubes, hypercubes, ...

Les différentes dimensions de la mémoire sont par exemple : l'amplitude, la fréquence, le temps, l'azimut,... On pourra ainsi accéder pour un temps donné, aux amplitudes et aux fréquences correspondantes... (Exploitation multisenseurs...)

- LES RESEAUX D'INTERCONNFXION - un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

La structure d'une telle mémoire peut être réalisée à l'aide d'un réseau SIMD dont les permutations permettent d'accéder en parallèle aux éléments d'un même "patron" : ligne, colonne, plan, cube...

#### 6 - CONCLUSIONS

L'évolution de la technologie des composants numériques en matière de traitement du signal impose de nouvelles architectures qui doivent autoriser la coopération d'un grand nombre de processeurs élémentaires sur le même traitement.

Les réseaux d'interconnexion qui étaient jusqu'à présnet très coûteux et peu performants s'imposent aujourd'hui grâce à de nouveaux développements théoriques (réseau Bénés,  $\Omega$ ,...) et technologiques (MSI spécifiques, logique multivaluée...).

Les différents types de réseaux d'interconnexion, leurs performances et leurs applications ont été succintement exposés.

Une maquette pour un réseau de 16 abonnés de type  $\Omega$  et fonctionnant en mode asynchrone MIMD ou synchrone MSIMD est en cours de réalisation à la SINTRA-ALCATEL.

#### 7 - BIBLIOGRAPHIE

[1] , [2] Flynn - IEEE.T.C Vol C21 N°9 Sep. 72

[3] , J.P. Brassard colloque - IEEE.80 (La Baule)

"Path building in cellular partitioning networks"

[4] , D. Etiemble: These doctorat en sciences:

"Contribution à l'étude des circuits multivalus et de leurs utilisations" PARIS VI

[7] , J. LENFANT: "Parallel permutation of data":

"à Bénès network control algorithm for frequently used permutation"IEEE.T.C V.C-27 July 78

[5] , [8] , [9] , AUGUIN-BOERI: contrat SINTRA-LASSY [10] , Ensemble d'outils pour la conception assistée par ordinateur (GRETSI - NICE 1979)

[1] , Le préprocesseur de signal PPS colloque (GRETSI - NICE 1979)

LES RESEAUX D'INTERCONNEXION un outil d'assemblage des fonctions spécialisées en traitement de signal (\*).

LES RESEAUX D'INTERCONNEXION – un outil d'assemblage des fonctions spécialisées en traitement du signal (\*).

PLANCHE: 3

DISTRIBUTION DES RETARDS (Distribution uniforme des adresse de banc)

.